CWG機能を動作させて見ます

〔PICの動かせ方入門に戻る〕

CWG機能(Complementary Waveform Generator Module)は、12F1822で拡張ECCPの

ハーフブリッジPWMやステアリング制御と呼んでいた機能と同等な機能を提供しています。

12F1501のCWG機能よりは、16F1705のCOG機能と同等な感じです。

このモジュールには、ハーフブリッジ/フルブリッジ機能やステアリング制御(相補PWM出力)機能に、

PWMの周期に合わせて交互に信号を出力する"プッシュプルモード"も有る様です。

又、自動シャットダウン機能や波形の立上がり/立下り時のデッドバンドも細かく設定可能です。

但し、16F18313の場合のデッドバンドはハーフブリッジ/フルブリッジモードにのみ有効です。

ここの記事では、ステアリング制御(相補PWM出力)機能のみ書いて置きます。

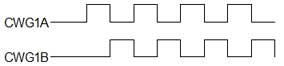

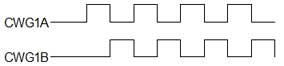

CWGの動作は、1つのパルスを入力し相補パルスに変換出力します。

※相補パルスとは

左図の様にCWG1AピンがHIGH時はCWG1BピンはLOWを

左図の様にCWG1AピンがHIGH時はCWG1BピンはLOWを

出力する様に反転させます(差動出力)、これを

相補PWM出力制御と言います。

CWGへの入力信号は、PWM5OUT/PWM6OUT/NCO1OUT/CLC1OUT/CLC2OUT/C1OUT/外部ピン

から選択出来ますが、ここではPWM5OUTから入力を行って見ます。

CWGには自動シャットダウン機能で外部ピンや内部からの信号により出力波形を一時停止状態に

出来ますが、今回は利用していません。

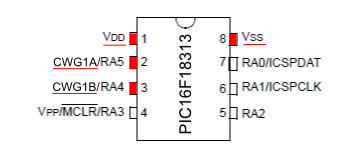

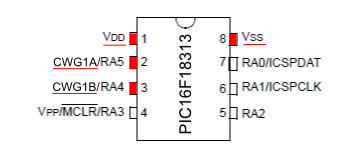

《PIC16F18313ピン構成》

CWGの出力するピンは、CWG1Aが2番(RA5)ピン

CWGの出力するピンは、CWG1Aが2番(RA5)ピン

から出力し、CWG1Bが3番(RA4)ピンから出力する

様にPPS機能で割り当てます。

尚、PICの1番ピンに電源+5V、

8番ピンに電源GND(-)を接続しています。

《サンプルプログラム》

CWGの入力源はPWM5で、PWM5の周期はTIMER2で1KHzを発生させPWMのデューティ比は50%です。

また、PICのシステムクロック(Fosc)は内蔵8MHzで行っています。

下記がプログラムソースです、

MPLAB X(V3.40) とMPLAB(R) XC8 C Compiler Version 1.38コンパイラを使用しています。

プロジェクトを作成して新規ファイルにコピーペーストして貼り付けて下さい。

---------------------------------------------------------------------

#include <xc.h>

// コンフィギュレーション1の設定

#pragma config FEXTOSC = OFF // 外部クロックは無効(OFF)

#pragma config RSTOSC = HFINT32 // 初期発振器は内部発振器(HFFRQx2倍)を選択(HFINT32)

#pragma config CLKOUTEN = OFF // CLKOUTピンをRA4ピンで使用する(OFF)

#pragma config CSWEN = OFF // NOSCとNDIVへの書き込みは許可しない(OFF)

#pragma config FCMEN = OFF // 外部クロック監視しない(OFF)

// コンフィギュレーション2の設定

#pragma config MCLRE = OFF // 外部リセット信号は使用せずにデジタル入力(RA3)ピンとする(OFF)

#pragma config PWRTE = ON // 電源ONから64ms後にプログラムを開始する(ON)

#pragma config WDTE = OFF // ウオッチドッグタイマー無し(OFF)

#pragma config LPBOREN = OFF // 低消費電力ブラウンアウトリセットは無効(OFF)

#pragma config BOREN = ON // 電源電圧降下常時監視機能ON(ON)

#pragma config PPS1WAY = OFF // ロック解除シーケンスを実行すれば何度でもPPSLOCKをセット/クリアできる

#pragma config STVREN = ON // スタックがオーバフローやアンダーフローしたらリセットをする(ON)

// コンフィギュレーション3の設定

#pragma config WRT = OFF // Flashメモリーを保護しない(OFF)

#pragma config LVP = OFF // 低電圧プログラミング機能使用しない(OFF)

// コンフィギュレーション4の設定

#pragma config CP = OFF // プログラムメモリーを保護しない(OFF)

#pragma config CPD = OFF // EEPROMデータメモリーを保護しない(OFF)

// メインの処理

void main()

{

OSCFRQbits.HFFRQ = 0b011 ; // 4MHzをx2で8MHzの周波数を生成

ANSELA = 0b00000000 ; // アナログは使用しない(すべてデジタルI/Oに割当てる)

TRISA = 0b00000000 ; // ピンは全て出力に割当てる(RA3は入力専用)

PORTA = 0b00000000 ; // 出力ピンの初期化(全てLOWにする)

// CWGの設定

RA5PPS = 0b00001000 ; // CWG1AはRA5ピンを使用する

RA4PPS = 0b00001001 ; // CWG1BはRA4ピンを使用する

CWG1CLKCON = 0b00000000 ; // クロックソースはFosc

CWG1DAT = 0b00000111 ; // PWM5をソースとする

CWG1STR = 0b00000011 ; // CWG1A/Bのステアリング操作はCWGデータ入力に割当て

CWG1CON1 = 0b00000010 ; // CWGはB端子を反転でA端子は正転

CWG1CON0 = 0b10000000 ; // CWGはONでステアリング非同期モードで動作

// PWM5の設定

PWM5CON = 0b10010000 ; // PWM5機能を使用する(output is active-high)

PWM5DCH = 64 ; // デューティ値は50%で初期化

PWM5DCL = 0 ;

T2CON = 0b00000010 ; // TMR2プリスケーラ値を16倍に設定

TMR2 = 0 ; // タイマー2カウンターを初期化

PR2 = 124 ; // PWMの周期を設定(1000Hzで設定)

TMR2ON = 1 ; // TMR2(PWM)スタート

while(1) {

}

}

---------------------------------------------------------------------

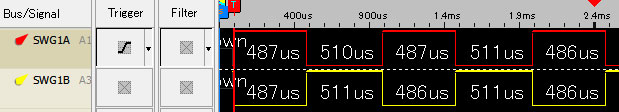

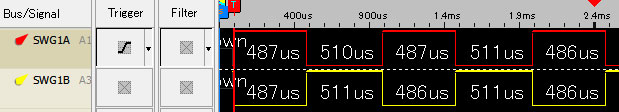

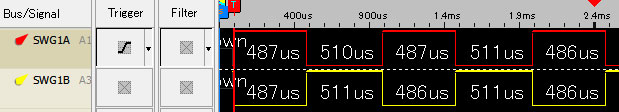

実行結果

このプログラム自体は設定のみなので、LED表示などの外部出力はないので何も変化は

無いですが、CWG1A/CWG1B端子にロジックアナライザを繋いで波形を表示させています。

上図が実行結果の表示です、

Aが正転(HIGH)の時Bは反転(LOW)していますね、もちろんBを正転でも出力出来ます。

PWM周期が1KHz(1000Hz)なので1サイクル(1000000us/1000Hz=1000us)は1msですね。

《レジスタの設定》

PWM5の設定

PWM5の設定は、12F1501のPWM1での説明ですがこちらを参照下さい。

尚、12F1501のデューティ値は10bitですが、16F18313では16bitとなります。

CWGの設定

CWGにて出力するピンを決めるには

RA5PPS = 0b00001000 ; // CWG1AはRA5ピンを使用する

RA4PPS = 0b00001001 ; // CWG1BはRA4ピンを使用する

もちろんANSEL/TRISにて使用するピンはデジタル出力に設定します。

他のピンRA0/RA1/RA2にも割り付けは可能です。

デッドバンドの設定は

CWG1DBR:立ち上がりエッジデッドバンド

CWG1DBF:立ち下がりエッジデッドバンド

立ち上がり/立ち下がりは、入力ソース(PWM1)のエッジから何クロック分出力を遅らせるのかを

設定します。

それぞれ6ビット[5:0]なので 0〜63 まで設定できます。

同じ設定値でも使用するクロック(Fosc/HFINTOSC)によってデッドバンドの長さが変わります。

尚、デッドバンドはハーフブリッジ/フルブリッジモードにのみ有効です。

CWG1CON0の構成

| ビッ

ト |

7 |

6 |

5 |

4 |

3 |

2 |

1 |

0 |

| 機能 |

EN |

LD |

|

|

|

MODE |

Bit 7:EN CWGモジュールの有効無効指定ビット

1:モジュールを使用する

0:モジュールを使用しない

Bit 6:LD CWGのデッドバンドバッファへのロードビット

1:このビットセット後にCWGデータはロードされる

0:バッファは変わりません

Bit 2-0:MODE 使用する操作モードの選択ビット

101:プッシュプルモード

100:ハーフブリッジモード

011:逆転フルブリッジモード

010:正転フルブリッジモード

001:同期ステアリングモード

000:非同期ステアリングモード

CWG1CON1の構成

| ビッ

ト |

7 |

6 |

5 |

4 |

3 |

2 |

1 |

0 |

| 機能 |

|

|

IN |

|

POLD |

POLC |

POLB |

POLA |

Bit 5:IN CWGデータ信号の入力状態表示ビット(読出しのみ)

Bit 3:POLD CWG1Dの出力極性指定ビット

1:極性を反転する

0:極性はそのまま

Bit 3:POLC CWG1Cの出力極性指定ビット

1:極性を反転する

0:極性はそのまま

Bit 3:POLB CWG1Bの出力極性指定ビット

1:極性を反転する

0:極性はそのまま

Bit 3:POLA CWG1Aの出力極性指定ビット

1:極性を反転する

0:極性はそのまま

CWG1CLKCONの構成

| ビッ

ト |

7 |

6 |

5 |

4 |

3 |

2 |

1 |

0 |

| 機能 |

|

|

|

|

|

|

|

CS |

Bit 0:CS CWGクロックのソース選択ビット

1:HFINTOSC(スリープ中も動作したままです)

0:Fosc

CWG1DATの構成

| ビッ

ト |

7 |

6 |

5 |

4 |

3 |

2 |

1 |

0 |

| 機能 |

|

|

|

|

DAT |

Bit 3-0:DAT CWG入力データの選択ビット

0000:外部ピンから入力(CWG1PPS)

0001:C1OUTから入力

0011:CCP1から入力

0100:CCP2から入力

0111:PWM5から入力

1000:PWM6から入力

1001:NCOから入力

1010:CLC1から入力

1011:CLC2から入力

CWG1STRの構成

| ビッ

ト |

7 |

6 |

5 |

4 |

3 |

2 |

1 |

0 |

| 機能 |

OVRD |

OVRC |

OVRB |

OVRA |

STRD |

STRC |

STRB |

STRA |

Bit 7:OVRD ビット

1:データは1で、出力はHIGH

0:データは0で、出力はLOW

Bit 6:OVRC ビット

1:データは1で、出力はHIGH

0:データは0で、出力はLOW

Bit 5:OVRB ビット

1:データは1で、出力はHIGH

0:データは0で、出力はLOW

Bit 4:OVRA ビット

1:データは1で、出力はHIGH

0:データは0で、出力はLOW

Bit 3:STRD ステアリングビットDを有効無効ビット

1:CWG1DはPOLDのデータで有効にする

0:OVRDビットのデータを使う

Bit 2:STRC ステアリングビットCを有効無効ビット

1:CWG1CはPOLCのデータで有効にする

0:OVRCビットのデータを使う

Bit 1:STRB ステアリングビットBを有効無効ビット

1:CWG1BはPOLBのデータで有効にする

0:OVRBビットのデータを使う

Bit 0:STRA ステアリングビットAを有効無効ビット

1:CWG1AはPOLAのデータで有効にする

0:OVRAビットのデータを使う

CWG1AS0/CWG1AS1の構成

自動シャットダウン関連のレジスタです、説明はデータシートを見て下さい。

《その他》

【きむ茶工房ガレージハウス】

Copyright (C) 2006-2016 Shigehiro Kimura All Rights Reserved.

左図の様にCWG1AピンがHIGH時はCWG1BピンはLOWを

左図の様にCWG1AピンがHIGH時はCWG1BピンはLOWを CWGの出力するピンは、CWG1Aが2番(RA5)ピン

CWGの出力するピンは、CWG1Aが2番(RA5)ピン