COG機能を動作させて見ます

〔PICの動かせ方入門に戻る〕

16F1705のCOG(Complementary Output Generator:相補出力ジェネレータ)機能は、

12F1501でCWGと呼んでいた機能にブランキング及び位相制御を追加し拡張を行ったモジュールです。

なので、ハーフブリッジ/フルブリッジ機能やステアリング制御(相補PWM出力)機能に、

PWMの周期に合わせて交互に信号を出力する"プッシュプルモード"も有る様です。

又、自動シャットダウン機能や波形の立上がり/立下り時のデッドバンドも細かく設定可能です。

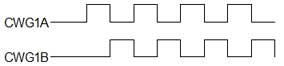

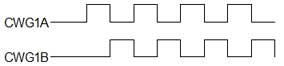

COGの動作は1つのパルスを入力し相補パルスに変換出力します。

※相補パルスとは

左図の様にCWG1AピンがHIGH時はCWG1BピンはLOWを

左図の様にCWG1AピンがHIGH時はCWG1BピンはLOWを

出力する様に反転させます(差動出力)、これを

相補PWM出力制御と言います。

(CWGをCOGと読み替えて下さい)

COGへの入力信号は、PWM3OUT/CCP1/CCP2/CLC1OUT/C1OUT/C2OUT/外部ピンから

選択出来ますが、ここではPWM3OUTから入力を行って見ます。

又、ハーフブリッジ/フルブリッジはモータ等を動作させる機能ですが、

ここではステアリング制御機能について記載します。

COGには自動シャットダウン機能で外部ピンや内部からの信号により出力波形を一時停止状態に

出来ますが、今回は記載していません。

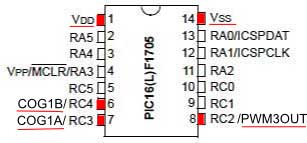

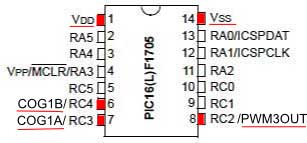

《PIC16F1705ピン構成》

左図がピンの構成図で、電源は5Vです。

左図がピンの構成図で、電源は5Vです。

16F1705はPWM3OUT/COG1A/COG1Bが

RA3のピン以外に割り振る事が可能ですが、

今回は左図の様に割り当てました。

PWM3OUTからピンに出力しなくても良いのですが、

ロジアナにて確認する為に出力しています。

《サンプルプログラム》

今回のプログラムは設定のみで何も接続していません、ロジックアナライザでの確認のみです。

PWM3OUTにLEDを接続すれば動作の確認にはなるでしょう。

尚、PICのシステムクロック(Fosc)は内蔵8MHzで行っています。

下記がプログラムソースです、

MPLAB X(V2.15) MPLAB(R) XC8 C Compiler Version 1.32コンパイラを使用しています。

プロジェクトを作成して新規ファイルにコピーペーストして貼り付けて下さい。

---------------------------------------------------------------------

#include <xc.h>

#define _XTAL_FREQ 8000000 // delay用に必要(クロック8MHzを指定)

// コンフィギュレーション1の設定

#pragma config FOSC = INTOSC // 内部クロック使用する(INTOSC)

#pragma config WDTE = OFF // ウオッチドッグタイマー無し(OFF)

#pragma config PWRTE = ON // 電源ONから64ms後にプログラムを開始する(ON)

#pragma config MCLRE = OFF // 外部リセット信号は使用せずにデジタル入力(RA3)ピンとする(OFF)

#pragma config CP = OFF // プログラムメモリーを保護しない(OFF)

#pragma config BOREN = ON // 電源電圧降下(BORV設定以下)常時監視機能ON(ON)

#pragma config CLKOUTEN = OFF // CLKOUTピンをRA4ピンで使用する(OFF)

#pragma config IESO = OFF // 内部から外部クロックへの切替えでの起動はなし(OFF)

#pragma config FCMEN = OFF // 外部クロック監視しない(OFF)

// コンフィギュレーション2の設定

#pragma config WRT = OFF // Flashメモリーを保護しない(OFF)

#pragma config PPS1WAY = OFF // ロック解除シーケンスを実行すれば何度でもPPSLOCKをセット/クリアできる

#pragma config ZCDDIS = ON // ゼロクロス検出回路は無効とする(ON)

#pragma config PLLEN = OFF // 動作クロックを32MHzでは動作させない(OFF)

#pragma config STVREN = ON // スタックがオーバフローやアンダーフローしたらリセットをする(ON)

#pragma config BORV = HI // 電源電圧降下常時監視電圧(2.7V)設定(HI)

#pragma config LPBOR = OFF // 低消費電力ブラウンアウトリセット(LPBOR_OFF)

#pragma config LVP = OFF // 低電圧プログラミング機能使用しない(OFF)

// メインの処理

void main()

{

OSCCON = 0b01110010 ; // 内部クロックは8MHzとする

ANSELA = 0b00000000 ; // AN0-AN3は使用しない全てデジタルI/Oとする

ANSELC = 0b00000000 ; // AN4-AN7は使用しない全てデジタルI/Oとする

TRISA = 0b00000000 ; // ピン(RA)は全て出力に割当てる(RA3は入力専用)

TRISC = 0b00000000 ; // ピン(RC)は全て出力に割当てる

PORTA = 0b00000000 ; // RA出力ピンの初期化(全てLOWにする)

PORTC = 0b00000000 ; // RC出力ピンの初期化(全てLOWにする)

// COGの設定

RC3PPS = 0b00001000 ; // RC3(7番)ピンからCOG1Aを出力する

RC4PPS = 0b00001001 ; // RC4(6番)ピンからCOG1Bを出力する

COG1CON0 = 0b10001000 ; // COGは非同期ステアリングモード、クロックはFosc

COG1CON1 = 0b00000001 ; // COG1Aは逆転でCOG1Bは正転で、デッドバンドはFoscを使う

COG1RIS = 0b01000000 ; // 入力の立ち上がりはPWM3OUTとする

COG1RSIM = 0b01000000 ; // PWM3OUTのLOWからHIGHでのエッジ立ち上がりで検出する

COG1FIS = 0b01000000 ; // 入力の立ち下がりはPWM3OUTとする

COG1FSIM = 0b01000000 ; // PWM3OUTのHIGHからLOWでのエッジ立ち上がりで検出する

COG1STR = 0b00000011 ; // COG1A/Bの出力はCOG1CON1の設定に従い波形を出力

COG1DBR = 0 ; // 波形立上がり時のデッドバンドはなし

COG1DBF = 0 ; // 波形立下がり時のデッドバンドはなし

COG1PHR = 0 ; // 波形立上がり時の出力実行遅延はしない

COG1PHF = 0 ; // 波形立下がり時の出力実行遅延はしない

// PWM3の設定

RC2PPS = 0b00001110 ; // RC2(8)ピンをPWM3OUT出力に割り当てる

PWM3CON = 0b11000000 ; // PWM3機能を使用する(output is active-high)

PWM3DCH = 64 ; // デューティ値は50%で初期化

PWM3DCL = 0 ;

T2CON = 0b00000010 ; // TMR2プリスケーラ値を16倍に設定

TMR2 = 0 ; // タイマー2カウンターを初期化

PR2 = 124 ; // PWMの周期を設定(1000Hzで設定)

TMR2ON = 1 ; // TMR2(PWM)スタート

while(1) {

}

}

---------------------------------------------------------------------

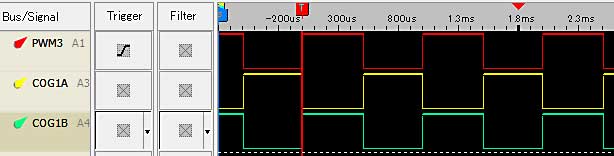

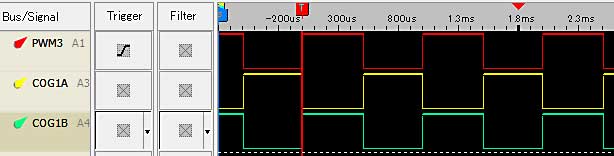

実行結果

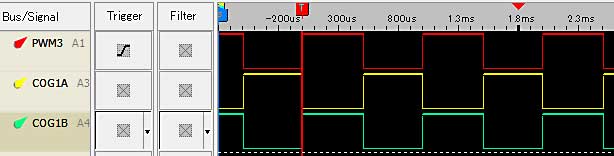

赤色波形のPWM3OUTを、COG機能でCOG1AとCOG1Bの相補パルスに変換出力していますね。

COG1BがPWM3OUT波形と同じ立ち上がり方向で、COG1Aが逆方向で設定されています。

デッドバンドは、ステアリングモードでは無効になるので設定していません、

デッドバンドが必要な場合は、ハーフブリッジ/フルブリッジモードで行います。

《レジスタの設定》

PWM3の設定

PWM3の設定はこちらを見て下さい。

CWGの設定

COG1CON0の構成

| ビッ

ト |

7 |

6 |

5 |

4 |

3 |

2 |

1 |

0 |

| 機能 |

G1EN |

G1LD |

|

G1CS |

G1MD |

Bit 7:G1EN COGモジュールの有効無効指定ビット

1 = モジュールを使用する

0 = モジュールを使用しない

Bit 6:G1LD COG1 Load Buffers bit

1 = Phase, blanking, and dead-band buffers to be loaded with register values on

next input events

0 = Register to buffer transfer is complete(デフォルト値)

COG動作中に位相、デッドバンド、ブランキングカウントを変更する場合に

バッファが必要らしぃ。(未確認)

Bit 4-3:G1CS COGで使用するクロックの選択ビット

10 = HFINTOSC(スリープ時にも動作させたい場合はこれを選択)

01 = Fosc(システムクロック)

00 = Fosc/4(システムクロックの4分の1)

Bit 2-0:G1MD COGの動作モード

101 = COG出力はプッシュプルモードで動作

100 = COG出力はハーフブリッジモードで動作

011 = COG出力はリバースフルブリッジモードで動作

010 = COG出力はフォワードフルブリッジモードで動作

001 = COG出力は同期ステアリングPWMモードで動作

000 = COG出力はステアリングPWMモードで動作

(今回設定の動作モード)

COG1CON1の構成

| ビッ

ト |

7 |

6 |

5 |

4 |

3 |

2 |

1 |

0 |

| 機能 |

G1RDBS |

G1FDBS |

|

|

G1POLD |

G1POLC |

G1POLB |

G1POLA |

Bit 7:G1RDBS 立ち上がりエッジデッドバンドのカウンターソース選択ビット

1 = 時間経過によりカウントを行う(1カウントあたり5ns)

0 = COGのクロック周波数にてカウントを行う

Bit 7:G1FDBS 立ち下がりエッジデッドバンドのカウンターソース選択ビット

1 = 時間経過によりカウントを行う(1カウントあたり5ns)

0 = COGのクロック周波数にてカウントを行う

Bit 3:G1POLD COG1D出力極性ビット

1 = D出力は極性を反転する(入力波形と逆の方向)

0 = D出力は通常の極性である(入力波形と同じ方向)

Bit 2:G1POLC COG1C出力極性ビット

1 = C出力は極性を反転する(入力波形と逆の方向)

0 = C出力は通常の極性である(入力波形と同じ方向)

Bit 1:G1POLB COG1B出力極性ビット

1 = B出力は極性を反転する(入力波形と逆の方向)

0 = B出力は通常の極性である(入力波形と同じ方向)

Bit 0:G1POLA COG1A出力極性ビット

1 = A出力は極性を反転する(入力波形と逆の方向)

0 = A出力は通常の極性である(入力波形と同じ方向)

デッドバンドの設定は

COG1DBR:立ち上がりエッジデッドバンドのカウンタ値レジスタ

COG1DBF:立ち下がりエッジデッドバンドのカウンタ値レジスタ

G1RDBS/G1FDBSを0で設定した場合

立ち上がり/立ち下がりは、入力ソース(今回PWM3)のエッジから何クロック分出力を遅らせるのかを

設定します。

カウンタ値はそれぞれ6ビットレジスタなので0〜63まで設定できます。

同じ設定値でも使用するクロック(Fosc/HFINTOSC)によってデッドバンドの長さが変わります。

G1RDBS/G1FDBSを1で設定した場合

立ち上がり/立ち下がりは、入力ソース(今回はPWM3)のエッジから何秒ほど出力を遅らせるのかを

設定します。

1カウントあたり5ns遅延します。

COG1RISの構成(立ち上がりイベントの入力ソース選択レジスタ)

| ビッ

ト |

7 |

6 |

5 |

4 |

3 |

2 |

1 |

0 |

| 機能 |

|

G1RIS6 |

G1RIS5 |

G1RIS4 |

G1RIS3 |

G1RIS2 |

G1RIS1 |

G1RIS0 |

Bit 6:G1RIS6 入力ソース6の選択ビット

1 = PWM3OUTを有効にする

0 = PWM3OUTは立ち上がりイベントに影響しない

Bit 5:G1RIS5 入力ソース5の選択ビット

1 = CCP2を有効にする

0 = CCP2は立ち上がりイベントに影響しない

Bit 4:G1RIS4 入力ソース4の選択ビット

1 = CCP1を有効にする

0 = CCP1は立ち上がりイベントに影響しない

Bit 3:G1RIS3 入力ソース3の選択ビット

1 = CLC1OUTを有効にする

0 = CLC1OUTは立ち上がりイベントに影響しない

Bit 2:G1RIS2 入力ソース2の選択ビット

1 = C2OUTを有効にする

0 = C2OUTは立ち上がりイベントに影響しない

Bit 1:G1RIS1 入力ソース1の選択ビット

1 = C1OUTを有効にする

0 = C1OUTは立ち上がりイベントに影響しない

Bit 0:G1RIS0 入力ソース0の選択ビット

1 = 外部ピン(COGPPSにての設定ピン)からの入力を有効にする

0 = 外部ピンからの入力は立ち上がりイベントに影響しない

COG1FISの構成(立ち下がりイベントの入力ソース選択レジスタ)

COG1RISのレジスタ構成と同様です。

COG1RSIMの構成(立ち上がりイベントの動作モード選択レジスタ)

| ビッ

ト |

7 |

6 |

5 |

4 |

3 |

2 |

1 |

0 |

| 機能 |

|

G1RSIM6 |

G1RSIM5 |

G1RSIM4 |

G1RSIM3 |

G1RSIM2 |

G1RSIM1 |

G1RSIM0 |

Bit 6:G1RSIM6 入力ソース6の選択ビット

1 = PWM3OUTがLOWからHIGHになったら出力を立上げる(エッジ検出)

0 = PWM3OUTの電圧がHIGHレベル(ヒステリシス)なら出力を立上げる(レベル検出)

Bit 5:G1RSIM5 入力ソース5の選択ビット

1:CCP2がLOWからHIGHになったら出力を立上げる(エッジ検出)

0:CCP2の電圧がHIGHレベル(ヒステリシス)なら出力を立上げる(レベル検出)

Bit 4:G1RSIM4 入力ソース4の選択ビット

1:CCP1がLOWからHIGHになったら出力を立上げる(エッジ検出)

0:CCP1の電圧がHIGHレベル(ヒステリシス)なら出力を立上げる(レベル検出)

Bit 3:G1RSIM3 入力ソース3の選択ビット

1:CLC1OUTがLOWからHIGHになったら出力を立上げる(エッジ検出)

0:CLC1OUTの電圧がHIGHレベル(ヒステリシス)なら出力を立上げる(レベル検出)

Bit 2:G1RSIM2 入力ソース2の選択ビット

1:C2OUTがLOWからHIGHになったら出力を立上げる(エッジ検出)

0:C2OUTの電圧がHIGHレベル(ヒステリシス)なら出力を立上げる(レベル検出)

Bit 1:G1RSIM1 入力ソース1の選択ビット

1:C1OUTがLOWからHIGHになったら出力を立上げる(エッジ検出)

0:C1OUTの電圧がHIGHレベル(ヒステリシス)なら出力を立上げる(レベル検出)

Bit 0:G1RSIM0 入力ソース0の選択ビット

1:外部ピンがLOWからHIGHになったら出力を立上げる(エッジ検出)

0:外部ピンの電圧がHIGHレベル(ヒステリシス)なら出力を立上げる(レベル検出)

※ 通常は"エッジ検出"で良いと思うがぁ、.....

電圧のしきい値での"レベル検出"はどんな時にセットするのか今一つ不明です。

COG1FSIMの構成(立ち下がりイベントの動作モード選択レジスタ)

COG1RSIMのレジスタ構成と同様です。

COG1STRの構成(ステアリング制御レジスタ)

| ビッ

ト |

7 |

6 |

5 |

4 |

3 |

2 |

1 |

0 |

| 機能 |

G1SDATD

|

G1SDATC |

G1SDATB |

G1SDATA |

G1STRD |

G1STRC |

G1STRB |

G1STRA |

Bit 7:G1SDATD G1STRDが"0"時に出力(静的出力)するビットデータ

1:データDはHIGHとする

0:データDLOWとする

Bit 6:G1SDATC G1STRCが"0"時に出力(静的出力)するビットデータ

1:データCはHIGHとする

0:データCLOWとする

Bit 5:G1SDATB G1STRBが"0"時に出力(静的出力)するビットデータ

1:データBはHIGHとする

0:データBLOWとする

Bit 4:G1SDATA G1STRAが"0"時に出力(静的出力)するビットデータ

1:データAはHIGHとする

0:データALOWとする

Bit 3:G1STRD COG1Dのステアリング制御ビット

1:G1POLDの極性制御に従い波形を出力(動的出力)する

0:G1SDATDの設定データでHIGHかLOWを出力(静的出力)する

Bit 3:G1STRC COG1Cのステアリング制御ビット

1:G1POLCの極性制御に従い波形を出力(動的出力)する

0:G1SDATCの設定データでHIGHかLOWを出力(静的出力)する

Bit 3:G1STRB COG1Bのステアリング制御ビット

1:G1POLBの極性制御に従い波形を出力(動的出力)する

0:G1SDATBの設定データでHIGHかLOWを出力(静的出力)する

Bit 3:G1STRA COG1Aのステアリング制御ビット

1:G1POLAの極性制御に従い波形を出力(動的出力)する

0:G1SDATAの設定データでHIGHかLOWを出力(静的出力)する

COG1ASD0/COG1ASD1の構成

自動シャットダウン関連のレジスタです。

外部ピン(COGINPPS)、コンパレータ(C1OUT/C2OUT)、CLC(CLC2OUT)、レジスタビットのON/OFF等

からCOGの出力を一時中断する事が可能です。(未実験)

COG1BLKR/COG1BLKFの構成

入力波形のブランキングにマスクを掛ける事が出来るらしい、これにより電気部品のターン・オン/オフ

によって生じる電気的過渡現象を防止する事である、とデータシートには書いて有る様な。(未実験)

COG1PHR/COG1PHFの構成

入力波形の立上がり/立下がり時に出力動作を行うが、この動作を遅らせる事が出来る機能です。

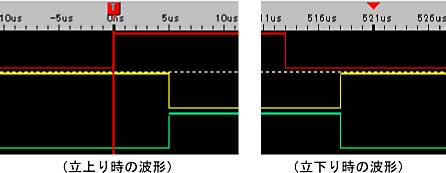

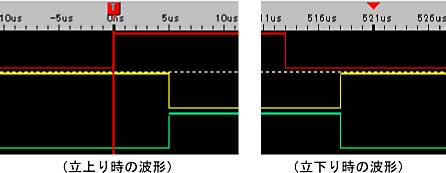

下図は、COG1PHR = 40 / COG1PHF = 40 で動作させた場合の波形です。

入力波形の立上がり時にFosc(COGクロック)の何個分遅らせるか指定(0〜63)できます。

COG1PHR = 40 設定なので

1/8MHz * 40 = 125ns * 40 = 5us です。

《その他》

CWGからCOG機能になって、入力ソースを混ぜたり、立上りと立下りで入力ソースを分けたりが

出来る様になったり、立上りと立下り時でのエッジ制御機能が増えたりしていますがぁ、

機能が増えるたびにレジスタも増えて設定などが大変ですよねぇMicrochipさん。

【きむ茶工房ガレージハウス】

Copyright (C) 2006-2014 Shigehiro Kimura All Rights Reserved.

左図の様にCWG1AピンがHIGH時はCWG1BピンはLOWを

左図の様にCWG1AピンがHIGH時はCWG1BピンはLOWを 左図がピンの構成図で、電源は5Vです。

左図がピンの構成図で、電源は5Vです。